Family Computer Disk System: Difference between revisions

(Added info about disk side and block formats) |

TakuikaNinja (talk | contribs) (Link to the TNES format, which has FDS support.) |

||

| (112 intermediate revisions by 21 users not shown) | |||

| Line 1: | Line 1: | ||

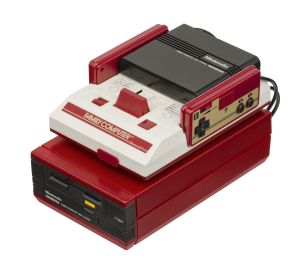

The '''Famicom Disk System''' | [[File:Nintendo-Famicom-Disk-System.jpg|300px|thumb|right|Famicom, FDS RAM adapter, and FDS disk drive]] | ||

Unfortunately for Nintendo, it also reduced the pirates' cost of making copies of games. | <div class="infobox"> | ||

<div style="text-align: center">'''FDS'''</div> | |||

{| class="oddf0 floatright" | |||

| '''Company''' | |||

| Nintendo | |||

|- | |||

| '''Complexity''' | |||

| ASIC | |||

|- | |||

| '''Pinout''' | |||

| [[RP2C33 pinout]] | |||

|- | |||

| '''BIOS PRG ROM size''' | |||

| 8K | |||

|- | |||

| '''PRG RAM capacity''' | |||

| 32K | |||

|- | |||

| '''CHR capacity''' | |||

| 8K | |||

|- | |||

| '''Disk capacity''' | |||

| ~64K per side | |||

|- | |||

| '''Mirroring''' | |||

| H or V, switchable | |||

|- | |||

| '''Bus conflicts''' | |||

| No | |||

|- | |||

| '''IRQ''' | |||

| Yes | |||

|- | |||

| '''Audio''' | |||

| Yes | |||

|}</div> | |||

The '''Famicom Disk System''' is a Japan-exclusive storage device for the Famicom, designed to reduce Nintendo's cost of making copies of games by switching from mask [[ROM]] chips to a storage medium based on Mitsumi's Quick Disk. | |||

Unfortunately for Nintendo, it also reduced the pirates' cost of making copies of games. Games are stored on one or multiple disk sides. The [[FDS BIOS]] is used to load data from disks to PRG RAM or VRAM, and games can execute from there. | |||

== | == Hardware == | ||

The | The Famicom disk system comes in two parts: The disk drive and the RAM adapter. | ||

The | The RAM adapter is a special shaped cartridge that contains the RAM chips and an ASIC with DRAM controller, IRQ hardware, sound generation hardware, serial interface for the disk drive, and parallel port. The Disk Drive has to be powered separately and is only connected to the Famicom/NES via a [[FDS RAM adaptor cable pinout|serial cable]] to the RAM adapter. | ||

Most disk drives contain two motors: a spindle motor that spins the disk at a specific speed, and a stepper motor which moves the read/write head between each circular data track. By comparison, the FDS only contains a single motor that does both at once, so it instead stores the data in a single spiral-shaped track. There is a mechanism that detects when the head reaches the end of the disc and makes it return to the start (making an audible click). Because of this limitation, random access to the disc is impossible, making FDS disk drive data access behave similarly to a reel of tape (but ''much'' faster). Data can only be accessed by spinning the disc, waiting for the head to reach the inner edge of the disc, then waiting again until the desired data file is reached. A complete cycle through the entire disc takes about 7 seconds. | |||

The disc drive only contains basic electronics, there is no "intelligence" in it; therefore, the serial interface almost directly represents what is stored on the disc. | |||

== | === Disks === | ||

The FDS disk is a modified version of the Mitsumi Quick Disk. | |||

See: | |||

* [[FDS disk format]] - the disk data format and file structure | |||

* [[FDS file format]] (.FDS) - an archival file format for storing and emulating FDS disks | |||

== Banks == | |||

All Banks are fixed | |||

* PPU $0000-$1FFF: 8k CHR RAM | |||

* CPU $6000-$DFFF: 32k PRG RAM | |||

== | * CPU $E000-$FFFF: 8k BIOS PRG ROM | ||

== Registers == | == Registers == | ||

$402x registers are write-only | $402x registers are write-only, | ||

$403x registers are read-only | $403x registers are read-only | ||

=== Timer IRQ reload value low ($4020) === | |||

=== IRQ | |||

7 bit 0 | 7 bit 0 | ||

--------- | --------- | ||

LLLL LLLL | |||

|||| |||| | |||| |||| | ||

++++-++++- 8 LSB of IRQ | ++++-++++- 8 LSB of timer IRQ reload value | ||

=== IRQ | === Timer IRQ reload value high ($4021) === | ||

7 bit 0 | 7 bit 0 | ||

--------- | --------- | ||

LLLL LLLL | |||

|||| |||| | |||| |||| | ||

++++-++++- 8 MSB of IRQ | ++++-++++- 8 MSB of timer IRQ reload value | ||

Unlike $4022, $4020 and $4021 are not affected by the $4023.0 (disk registers enabled) flag - the reload value can be altered even when disk registers are disabled. | |||

=== IRQ | === Timer IRQ control ($4022) === | ||

7 bit 0 | 7 bit 0 | ||

--------- | --------- | ||

xxxx | xxxx xxER | ||

| | || | ||

+-- | |-- Timer IRQ Repeat Flag | ||

+-- Timer IRQ Enabled | |||

When $4022 is written to with bit 1 (IRQ enabled) set, the reload value is copied into the IRQ's counter. | |||

Each CPU clock cycle the counter is decremented by one if the enable flag is set. | |||

When the counter's value is 0 and the IRQ enable flag is on, the following happens on every CPU cycle: | |||

* An IRQ is generated. | |||

* The IRQ counter is reset to its reload value (contained in $4020+$4021) | |||

* If the IRQ repeat flag is NOT set, the IRQ enabled flag is cleared and the counter stops. | |||

Notes: | |||

* This register is affected by the $4023.0 (Enable disk I/O registers) flag - if disk registers are disabled, it is impossible to start the IRQ counter (writing to $4022 has no effect). | |||

* Clearing $4023.0 will immediately stop the IRQ counter and acknowledge any pending timer IRQs. | |||

* Writing to $4022 with bit 1 (IRQ enabled) cleared will stop the IRQ counter and acknowledge any pending timer IRQs. | |||

* Enabling timer IRQs when the reload value is set to 0 will cause an IRQ immediately. Doing this with the repeat flag enabled will cause an infinite loop of IRQs on every CPU cycle. | |||

* Since the disk transfer routine also uses IRQs, it's very important to disable timer IRQs before doing any access to the disk. | |||

There are only 3 known ways to acknowledge the timer IRQ: | |||

* Read $4030 | |||

* Disable timer IRQs by writing to $4022 | |||

* Disable disk registers by writing to $4023 | |||

=== Master I/O enable ($4023) === | === Master I/O enable ($4023) === | ||

| Line 147: | Line 124: | ||

+-- Enable sound I/O registers | +-- Enable sound I/O registers | ||

The FDS BIOS writes $00, then $83 to it during reset. The purpose of bit 7 is unknown. | |||

Disabling disk registers disables both disk and timer IRQs. | |||

=== Write data register ($4024) === | === Write data register ($4024) === | ||

The data that this register is programmed with will be the next 8-bit quantity to load into the shift register (next time the byte transfer flag raises), and to be shifted out and appear on pin 5 of the RAM | The data that this register is programmed with will be the next 8-bit quantity to load into the shift register (next time the byte transfer flag raises), and to be shifted out and appear on pin 5 of the RAM adapter cable (2C33 pin 52). | ||

Writing to this register acknowledges disk IRQs.{{Citation needed}} | |||

=== FDS Control ($4025) === | === FDS Control ($4025) === | ||

7 bit 0 | 7 bit 0 | ||

--------- | --------- | ||

IE1C MRDT | |||

|||| |||| | |||| |||| | ||

|||| |||+- | |||| |||+- Transfer Reset | ||

|||| ||| 0: | |||| ||| 0: Reset transfer timing to the initial state. | ||

|||| ||+-- Drive Motor Control (0: start, 1: stop) | |||

|||| |+--- Transfer Mode (0: write; 1: read) | |||

|||| +---- Mirroring (0: vertical; 1: horizontal) | |||

|||| |+-- | |||+------ CRC Transfer Control (1: transfer CRC value) | ||

|||| | | ||+------- Unknown, always set to '1' | ||

|||| +---- Mirroring (0: | |+-------- CRC Enabled (0: disable/reset, 1: enable) | ||

|||+------ CRC | +--------- Interrupt Enabled | ||

||+------- | 1: Generate an IRQ every time the byte transfer flag is raised. | ||

|+-------- | |||

+--------- Interrupt | |||

1: | |||

Notes: | |||

* Disabling the CRC resets its state. The FDS BIOS disables the CRC between file blocks, then enables it before accessing each file block to calculate/verify their CRC values. | |||

* To change the mirroring on the fly, a read-modify-write of its [[FDS BIOS#Zero-page variables|mirror]] should be done to prevent altering unrelated bits. | |||

Writing to this register acknowledges disk IRQ. | |||

=== External connector ($4026) === | === External connector ($4026) === | ||

| Line 180: | Line 160: | ||

Output of expansion terminal where there's a shutter on the back of the ram card. The outputs of $4026 (open-collector with 4.7K ohm pull-ups (except on bit 7)), are shared with the inputs on $4033. | Output of expansion terminal where there's a shutter on the back of the ram card. The outputs of $4026 (open-collector with 4.7K ohm pull-ups (except on bit 7)), are shared with the inputs on $4033. | ||

=== Disk Status | === Disk Status register ($4030) === | ||

7 bit 0 | 7 bit 0 | ||

--------- | --------- | ||

IExB xxTD | IExB xxTD | ||

|| | || | |||

|| | |+- Timer Interrupt (1: an IRQ occurred) | |||

|| | +-- Byte transfer flag. Set every time 8 bits have been transferred between the RAM adaptor & disk drive (service $4024/$4031). | |||

|| | Reset when $4024, $4031, or $4030 has been serviced. | |||

|| +------ CRC control (0: CRC passed; 1: CRC error) | |||

|+-------- End of Head (1 when disk head is on the most inner track) | |+-------- End of Head (1 when disk head is on the most inner track) | ||

+--------- Disk Data Read/Write Enable (1 when disk is readable/ | +--------- Disk Data Read/Write Enable (1 when disk is readable/writeable) | ||

Reading this register acknowledges timer and disk IRQs. | |||

=== Read data register ($4031) === | === Read data register ($4031) === | ||

This register is loaded with the contents of an internal shift register every time the byte transfer flag raises. The shift register | This register is loaded with the contents of an internal shift register every time the byte transfer flag raises. The shift register receives its serial data via pin 9 of the RAM adapter cable (2C33 pin 51). | ||

Reading this register acknowledges disk IRQs. | |||

=== Disk drive status register ($4032) === | === Disk drive status register ($4032) === | ||

| Line 202: | Line 186: | ||

||| | ||| | ||

||+- Disk flag (0: Disk inserted; 1: Disk not inserted) | ||+- Disk flag (0: Disk inserted; 1: Disk not inserted) | ||

|+-- Ready flag (0: Disk | |+-- Ready flag (0: Disk readу; 1: Disk not ready) | ||

+--- Protect flag (0: Not write protected; 1: Write protected or disk ejected) | +--- Protect flag (0: Not write protected; 1: Write protected or disk ejected) | ||

Reading this register acknowledges disk IRQs.{{Citation needed}} | |||

=== External connector read ($4033) === | === External connector read ($4033) === | ||

| Line 211: | Line 197: | ||

|||| |||| | |||| |||| | ||

|+++-++++- Input from expansion terminal where there's a shutter on the back of the ram card. | |+++-++++- Input from expansion terminal where there's a shutter on the back of the ram card. | ||

+--------- Battery status (0: | +--------- Battery status (0: Voltage is low; 1: Good). | ||

When a bit is clear in $4026 port it will read back as '0' here (including battery bit) because of how open collector input works. | When a bit is clear in $4026 port it will read back as '0' here (including battery bit) because of how open collector input works. Battery bit should be checked when the motor is on, otherwise it always will be read as 0. | ||

=== Sound ($4040-$ | === Sound ($4040-$4092) === | ||

For details on sound information, see [[FDS_audio|FDS audio]]. | For details on sound information, see [[FDS_audio|FDS audio]]. | ||

== | == BIOS == | ||

The FDS contains a fixed 8KB BIOS at $E000-FFFF. This controls the Famicom at power-on and reset, dispatches the NMI and IRQ, and offers an API for accessing the [[FDS disk format|data on disk]]. | |||

See: [[FDS BIOS]] | |||

== See Also == | |||

* [[FDS BIOS]] | |||

* [[FDS disk format]] | |||

* [[FDS file format]] ('''.FDS''') | |||

* [[FDS audio]] | |||

* [[FDS RAM adaptor cable pinout]] | |||

* [[RP2C33 pinout]] | |||

* [[iNES mapper 020|iNES mapper 20]] - Reserved for FDS dumps, but not widely used for it. | |||

* [[TNES]] - Nintendo 3DS Virtual Console ROM format with support for FDS disk images. | |||

* [https://github.com/bbbradsmith/NES-ca65-example/tree/fds Github repository:] Simple FDS example for ca65 | |||

* [//forums.nesdev.org/viewtopic.php?p=194826#p194826 Forum post:] Skipping the FDS license screen | |||

== References == | |||

* [//nesdev.org/FDS%20technical%20reference.txt FDS technical reference.txt] by Brad Taylor (old/outdated) | |||

* [http://nesdev. | * [http://cmpslv2.starfree.jp/Famic/Famdis.htm Enri's Famicom Disk System page] (Japanese) | ||

* [https://web.archive.org/web/20091023182159/http://www2.odn.ne.jp/~haf09260/Famic/Famdis.htm Enri's Famicom Disk System page] (Japanese) (old/outdated) | |||

* [//nesdev.org/fds-nori.txt fds-nori.txt] - FDS reference in Japanese by Nori (old/outdated) | |||

* [https://www.chrismcovell.com/software.html FDS List] by ccovell - command line utility to inspect FDS disk image contents. | |||

* [https://www.chrismcovell.com/fds-lister.html FDS Lister] by ccovell - utility to inspect FDS disk contents that runs on an FDS. | |||

* [//forums.nesdev.org/viewtopic.php?p=194867#p194867 Forum post]: .fds format: Can checksums be heuristically detected? - Includes a CRC implementation in C. | |||

* [//forums.nesdev.org/viewtopic.php?f=3&t=16507 Forum post]: FDS IRQ reload flag/value | |||

<references/> | |||

[[Category:Mappers using $4020-$5FFF]][[Category:Mappers with cycle IRQs]] | |||

Latest revision as of 07:51, 20 April 2024

| Company | Nintendo |

| Complexity | ASIC |

| Pinout | RP2C33 pinout |

| BIOS PRG ROM size | 8K |

| PRG RAM capacity | 32K |

| CHR capacity | 8K |

| Disk capacity | ~64K per side |

| Mirroring | H or V, switchable |

| Bus conflicts | No |

| IRQ | Yes |

| Audio | Yes |

The Famicom Disk System is a Japan-exclusive storage device for the Famicom, designed to reduce Nintendo's cost of making copies of games by switching from mask ROM chips to a storage medium based on Mitsumi's Quick Disk. Unfortunately for Nintendo, it also reduced the pirates' cost of making copies of games. Games are stored on one or multiple disk sides. The FDS BIOS is used to load data from disks to PRG RAM or VRAM, and games can execute from there.

Hardware

The Famicom disk system comes in two parts: The disk drive and the RAM adapter.

The RAM adapter is a special shaped cartridge that contains the RAM chips and an ASIC with DRAM controller, IRQ hardware, sound generation hardware, serial interface for the disk drive, and parallel port. The Disk Drive has to be powered separately and is only connected to the Famicom/NES via a serial cable to the RAM adapter.

Most disk drives contain two motors: a spindle motor that spins the disk at a specific speed, and a stepper motor which moves the read/write head between each circular data track. By comparison, the FDS only contains a single motor that does both at once, so it instead stores the data in a single spiral-shaped track. There is a mechanism that detects when the head reaches the end of the disc and makes it return to the start (making an audible click). Because of this limitation, random access to the disc is impossible, making FDS disk drive data access behave similarly to a reel of tape (but much faster). Data can only be accessed by spinning the disc, waiting for the head to reach the inner edge of the disc, then waiting again until the desired data file is reached. A complete cycle through the entire disc takes about 7 seconds.

The disc drive only contains basic electronics, there is no "intelligence" in it; therefore, the serial interface almost directly represents what is stored on the disc.

Disks

The FDS disk is a modified version of the Mitsumi Quick Disk.

See:

- FDS disk format - the disk data format and file structure

- FDS file format (.FDS) - an archival file format for storing and emulating FDS disks

Banks

All Banks are fixed

- PPU $0000-$1FFF: 8k CHR RAM

- CPU $6000-$DFFF: 32k PRG RAM

- CPU $E000-$FFFF: 8k BIOS PRG ROM

Registers

$402x registers are write-only, $403x registers are read-only

Timer IRQ reload value low ($4020)

7 bit 0 --------- LLLL LLLL |||| |||| ++++-++++- 8 LSB of timer IRQ reload value

Timer IRQ reload value high ($4021)

7 bit 0 --------- LLLL LLLL |||| |||| ++++-++++- 8 MSB of timer IRQ reload value

Unlike $4022, $4020 and $4021 are not affected by the $4023.0 (disk registers enabled) flag - the reload value can be altered even when disk registers are disabled.

Timer IRQ control ($4022)

7 bit 0

---------

xxxx xxER

||

|-- Timer IRQ Repeat Flag

+-- Timer IRQ Enabled

When $4022 is written to with bit 1 (IRQ enabled) set, the reload value is copied into the IRQ's counter. Each CPU clock cycle the counter is decremented by one if the enable flag is set.

When the counter's value is 0 and the IRQ enable flag is on, the following happens on every CPU cycle:

- An IRQ is generated.

- The IRQ counter is reset to its reload value (contained in $4020+$4021)

- If the IRQ repeat flag is NOT set, the IRQ enabled flag is cleared and the counter stops.

Notes:

- This register is affected by the $4023.0 (Enable disk I/O registers) flag - if disk registers are disabled, it is impossible to start the IRQ counter (writing to $4022 has no effect).

- Clearing $4023.0 will immediately stop the IRQ counter and acknowledge any pending timer IRQs.

- Writing to $4022 with bit 1 (IRQ enabled) cleared will stop the IRQ counter and acknowledge any pending timer IRQs.

- Enabling timer IRQs when the reload value is set to 0 will cause an IRQ immediately. Doing this with the repeat flag enabled will cause an infinite loop of IRQs on every CPU cycle.

- Since the disk transfer routine also uses IRQs, it's very important to disable timer IRQs before doing any access to the disk.

There are only 3 known ways to acknowledge the timer IRQ:

- Read $4030

- Disable timer IRQs by writing to $4022

- Disable disk registers by writing to $4023

Master I/O enable ($4023)

7 bit 0

---------

xxxx xxSD

||

|+- Enable disk I/O registers

+-- Enable sound I/O registers

The FDS BIOS writes $00, then $83 to it during reset. The purpose of bit 7 is unknown.

Disabling disk registers disables both disk and timer IRQs.

Write data register ($4024)

The data that this register is programmed with will be the next 8-bit quantity to load into the shift register (next time the byte transfer flag raises), and to be shifted out and appear on pin 5 of the RAM adapter cable (2C33 pin 52).

Writing to this register acknowledges disk IRQs.[citation needed]

FDS Control ($4025)

7 bit 0

---------

IE1C MRDT

|||| ||||

|||| |||+- Transfer Reset

|||| ||| 0: Reset transfer timing to the initial state.

|||| ||+-- Drive Motor Control (0: start, 1: stop)

|||| |+--- Transfer Mode (0: write; 1: read)

|||| +---- Mirroring (0: vertical; 1: horizontal)

|||+------ CRC Transfer Control (1: transfer CRC value)

||+------- Unknown, always set to '1'

|+-------- CRC Enabled (0: disable/reset, 1: enable)

+--------- Interrupt Enabled

1: Generate an IRQ every time the byte transfer flag is raised.

Notes:

- Disabling the CRC resets its state. The FDS BIOS disables the CRC between file blocks, then enables it before accessing each file block to calculate/verify their CRC values.

- To change the mirroring on the fly, a read-modify-write of its mirror should be done to prevent altering unrelated bits.

Writing to this register acknowledges disk IRQ.

External connector ($4026)

Output of expansion terminal where there's a shutter on the back of the ram card. The outputs of $4026 (open-collector with 4.7K ohm pull-ups (except on bit 7)), are shared with the inputs on $4033.

Disk Status register ($4030)

7 bit 0 --------- IExB xxTD || | || || | |+- Timer Interrupt (1: an IRQ occurred) || | +-- Byte transfer flag. Set every time 8 bits have been transferred between the RAM adaptor & disk drive (service $4024/$4031). || | Reset when $4024, $4031, or $4030 has been serviced. || +------ CRC control (0: CRC passed; 1: CRC error) |+-------- End of Head (1 when disk head is on the most inner track) +--------- Disk Data Read/Write Enable (1 when disk is readable/writeable)

Reading this register acknowledges timer and disk IRQs.

Read data register ($4031)

This register is loaded with the contents of an internal shift register every time the byte transfer flag raises. The shift register receives its serial data via pin 9 of the RAM adapter cable (2C33 pin 51).

Reading this register acknowledges disk IRQs.

Disk drive status register ($4032)

7 bit 0

---------

xxxx xPRS

|||

||+- Disk flag (0: Disk inserted; 1: Disk not inserted)

|+-- Ready flag (0: Disk readу; 1: Disk not ready)

+--- Protect flag (0: Not write protected; 1: Write protected or disk ejected)

Reading this register acknowledges disk IRQs.[citation needed]

External connector read ($4033)

7 bit 0 --------- BIII IIII |||| |||| |+++-++++- Input from expansion terminal where there's a shutter on the back of the ram card. +--------- Battery status (0: Voltage is low; 1: Good).

When a bit is clear in $4026 port it will read back as '0' here (including battery bit) because of how open collector input works. Battery bit should be checked when the motor is on, otherwise it always will be read as 0.

Sound ($4040-$4092)

For details on sound information, see FDS audio.

BIOS

The FDS contains a fixed 8KB BIOS at $E000-FFFF. This controls the Famicom at power-on and reset, dispatches the NMI and IRQ, and offers an API for accessing the data on disk.

See: FDS BIOS

See Also

- FDS BIOS

- FDS disk format

- FDS file format (.FDS)

- FDS audio

- FDS RAM adaptor cable pinout

- RP2C33 pinout

- iNES mapper 20 - Reserved for FDS dumps, but not widely used for it.

- TNES - Nintendo 3DS Virtual Console ROM format with support for FDS disk images.

- Github repository: Simple FDS example for ca65

- Forum post: Skipping the FDS license screen

References

- FDS technical reference.txt by Brad Taylor (old/outdated)

- Enri's Famicom Disk System page (Japanese)

- Enri's Famicom Disk System page (Japanese) (old/outdated)

- fds-nori.txt - FDS reference in Japanese by Nori (old/outdated)

- FDS List by ccovell - command line utility to inspect FDS disk image contents.

- FDS Lister by ccovell - utility to inspect FDS disk contents that runs on an FDS.

- Forum post: .fds format: Can checksums be heuristically detected? - Includes a CRC implementation in C.

- Forum post: FDS IRQ reload flag/value