NES 2.0 Mapper 368: Difference between revisions

From NESdev Wiki

Jump to navigationJump to search

m (Yung-8 -> Yung-08) |

NewRisingSun (talk | contribs) (update on which version is the parent of which) |

||

| Line 2: | Line 2: | ||

[[File:YUNG8-front.jpg|thumb|PCB front]] | [[File:YUNG8-front.jpg|thumb|PCB front]] | ||

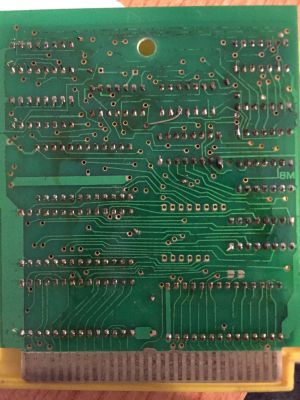

[[File:YUNG8-back.jpg|thumb|PCB back (mirrored, pin 31 on the left)]] | [[File:YUNG8-back.jpg|thumb|PCB back (mirrored, pin 31 on the left)]] | ||

NES 2.0 Mapper 368 denotes the Yung-08 cartridge conversion PCB of the disk system game ''Super Mario Bros. 2 (Japan)''. It is | NES 2.0 Mapper 368 denotes the Yung-08 cartridge conversion PCB of the disk system game ''Super Mario Bros. 2 (Japan)''. It is the "parent" of the [[INES Mapper 050|N-32]] and [[NES 2.0 Mapper 357|Mr. Mary 2]] conversions, as both retain (jumped-over) [[#Latch_read_.28.244122.2C_read.29|protection-reading code]] from this version. | ||

There are two 32 KiB PRG-ROM chips, one 2 KiB PRG-ROM, and one 8 KiB CHR-ROM chip. The ROM image's 128 KiB PRG-ROM part is arranged as follows: | There are two 32 KiB PRG-ROM chips, one 2 KiB PRG-ROM, and one 8 KiB CHR-ROM chip. The ROM image's 128 KiB PRG-ROM part is arranged as follows: | ||

Latest revision as of 07:49, 27 August 2019

NES 2.0 Mapper 368 denotes the Yung-08 cartridge conversion PCB of the disk system game Super Mario Bros. 2 (Japan). It is the "parent" of the N-32 and Mr. Mary 2 conversions, as both retain (jumped-over) protection-reading code from this version.

There are two 32 KiB PRG-ROM chips, one 2 KiB PRG-ROM, and one 8 KiB CHR-ROM chip. The ROM image's 128 KiB PRG-ROM part is arranged as follows:

- Offset $00000: First PRG-ROM chip (32 KiB)

- Offset $08000: Second PRG-ROM chip (32 KiB)

- Offset $10000: Third PRG-ROM chip, repeated 32 times (64 KiB)

Banks

- CPU $6000-$7FFF: 8 KiB PRG-ROM bank, fixed to #2

- CPU $8000-$9FFF: 8 KiB PRG-ROM bank, fixed to #1

- CPU $A000-$BFFF: 8 KiB PRG-ROM bank, fixed to #0

- CPU $C000-$DFFF: 8 KiB PRG-ROM bank, switchable

- CPU $E000-$FFFF: 8 KiB PRG-ROM bank, fixed to #8 (2 KiB PRG-ROM repeated four times)

- PPU $0000-$1FFF: unbanked 8 KiB CHR-ROM

Registers

PRG Bank Select ($4022, write)

Mask: $F1FF

Bit 7654 3210

---------

.... .CCC

+++- Select 8 KiB PRG-ROM bank at CPU $C000-$DFFF

The actual bank number is:

Value Bank# ------------ 0 4 1 3 2 5 3 3 4 6 5 3 6 7 7 3

Latch write/IRQ Control ($4122, write)

Mask: $F1FF

D~7654 3210

---------

..LL .L.I

|| | +- 0: Acknowledge and disable IRQ, reset counter

|| | | 1: Enable IRQ

++--+-+- Bits to be read-back

When enabled, the 12-bit IRQ counter increases on every M2 cycle until it overflows, upon which an IRQ is fired.

Latch read ($4122, read)

Mask: $F1FF

D~7654 3210

---------

10LL 1L1L

++--+-+- Latched bits

When holding the A button while pressing START to begin in World A-1, the game checks the latch's functionality and returns to the title screen if the check fails.